Hintergrund

Herkömmliche Mikrocontroller und CPU-basierte System-on-Chips (SoCs) sind zwar in hohem Maße programmierbar, jedoch hinsichtlich ihrer Energieeffizienz eingeschränkt. Ein Grund dafür ist der kontinuierliche Energieaufwand des Befehlsstroms. Rekonfigurierbare Arrays (FPGAs, CGRAs) können Daten mit einer höheren Energieeffizienz verarbeiten, sind jedoch schwer zu programmieren. Das beschriebene Konzept kombiniert die einfache Programmierbarkeit von RISC-Architekturen mit einer CGRA-ähnlichen hohen Energieeffizienz.

Technische Beschreibung

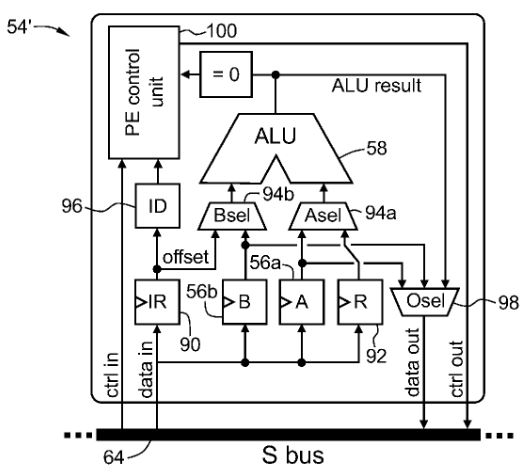

Die Architektur besteht aus einer Matrix von Verarbeitungselementen (PEs), von denen jedes Befehle decodiert und ausführt. Jedes PE verfügt über ein Befehlsregister, ALUs für arithmetische und logische Verarbeitungen, mehrere Speicherregister (A, B, R) sowie eine Steuereinheit für lokale Entscheidungslogik und Verzweigungen. Der S-Bus bildet die Datenpfade zwischen den Teilen des Arrays, während der M-Bus für die Kommunikation mit externen Einheiten, dem Speicher und einem Fragment Instance Manager (FIM) zuständig ist. Das System arbeitet auf Fragmentbasis, wobei Programmabschnitte in die Verarbeitungselemente geladen werden. Der FIM verwaltet die Ausführung, Speicherung und Wiederherstellung dieser Fragmente, um die Rechenlast dynamisch an die Hardware-Ressourcen anzupassen. Sein auf 32-Bit-Wörtern basierender Befehlssatz ermöglicht eine einfache Dekodierung, minimale Operandentypen und unterstützt die gleichzeitige Koordination von Daten- und Kontrollfluss.

Anwendungsmöglichkeiten

Die Technologie eignet sich besonders für Embedded-, Edge- und IoT-Systeme, bei denen sowohl Energieeffizienz als auch Programmierbarkeit entscheidend sind. Anwendungsbeispiele sind batteriebetriebene Sensorknoten und Signalverarbeitungsanwendungen.

Teil der schematischen Anordnung (© TU Berlin)