Background

Conventional microcontrollers and CPU-based Systems-on-Chips (SoCs) are highly programmable but limited in energy efficiency. One reason for this is the continuous energy overhead of the instruction stream. Reconfigurable arrays (FPGAs, CGRAs) can process data with a higher energy efficiency but are difficult to program. The concept described combines the easy programmability of RISC architectures with CGRA-like high energy efficiency.

Technical Description

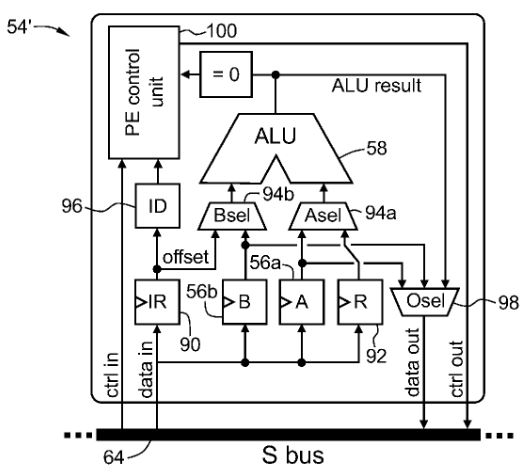

The architecture consists of a matrix of processing elements (PEs), each of which decodes and executes instructions. Each PE has an instruction register, ALUs for arithmetic and logical processing, several memory registers (A, B, R), a control unit for local decision logic and branches. The S-bus forms the data paths between parts of the array, while the M-bus is responsible for communication with external units, memory and a Fragment Instance Manager (FIM). The system operates on a fragment basis, with program sections being loaded into the processing elements. The FIM manages the execution, storage and recovery of these fragments in order to dynamically adapt computing loads to hardware resources. Its instruction set, based on 32-bit words, allows for simple decoding, minimal operand types and supports simultaneous data and control flow coordination.

Possible Applications

The technology is particularly suitable for embedded, edge and IoT systems where both energy efficiency and programmability are critical. Example applications include battery-powered sensor nodes and signal processing applications.

Part of schematic representation (© TU Berlin)